Znate li kako riješiti EMI problem kada se dizajnira višeslojni PCB?

Da ti kažem!

Postoji mnogo načina za rješavanje EMI problema.Moderne metode suzbijanja EMI uključuju: korištenje premaza za suzbijanje EMI, odabir odgovarajućih dijelova za suzbijanje EMI i dizajn simulacije EMI.Zasnovano na najosnovnijem rasporedu PCB-a, ovaj rad govori o funkciji PCB steka u kontroli EMI zračenja i vještinama dizajna PCB-a.

power bus

Skok izlaznog napona IC-a može se ubrzati postavljanjem odgovarajućeg kapacitivnosti blizu priključka napajanja IC-a.Međutim, ovo nije kraj problema.Zbog ograničenog frekventnog odziva kondenzatora, nemoguće je da kondenzator generira harmonijsku snagu potrebnu za čist IC izlaz u punom frekventnom opsegu.Osim toga, prelazni napon formiran na sabirnici napajanja će uzrokovati pad napona na oba kraja induktivnosti puta za razdvajanje.Ovi prolazni naponi su glavni izvori EMI smetnji uobičajenog moda.Kako možemo riješiti ove probleme?

U slučaju IC-a na našoj ploči, sloj napajanja oko IC-a može se smatrati dobrim visokofrekventnim kondenzatorom, koji može prikupiti energiju propuštenu diskretnim kondenzatorom koji daje energiju visoke frekvencije za čist izlaz.Osim toga, induktivnost dobrog sloja snage je mala, tako da je prolazni signal sintetiziran induktorom također mali, čime se smanjuje EMI zajedničkog moda.

Naravno, veza između sloja napajanja i pina napajanja IC mora biti što kraća, jer je rastuća ivica digitalnog signala sve brža i brža.Bolje ga je spojiti direktno na podlogu gdje se nalazi IC power pin, o čemu treba posebno razgovarati.

Da bi se kontrolisao EMI u zajedničkom modu, sloj snage mora biti dobro dizajniran par slojeva snage koji pomaže u razdvajanju i ima dovoljno nisku induktivnost.Neki ljudi će se možda pitati koliko je to dobro?Odgovor ovisi o sloju snage, materijalu između slojeva i radnoj frekvenciji (tj. funkcija vremena porasta IC).Općenito, razmak energetskih slojeva je 6 mil, a međusloj je FR4 materijal, tako da je ekvivalentna kapacitivnost po kvadratnom inču sloja napajanja oko 75 pF.Očigledno, što je manji razmak slojeva, to je veći kapacitet.

Nema mnogo uređaja sa vremenom porasta od 100-300ps, ali prema trenutnoj stopi razvoja IC-a, uređaji sa vremenom porasta u rasponu od 100-300ps će zauzimati veliki udio.Za krugove s vremenom porasta od 100 do 300 PS, razmak slojeva od 3 mil više nije primjenjiv za većinu primjena.Tada je potrebno usvojiti tehnologiju raslojavanja sa međuslojnim razmakom manjim od 1 mil, i zamijeniti FR4 dielektrični materijal materijalom visoke dielektrične konstante.Sada, keramika i plastika u posudama mogu zadovoljiti zahtjeve dizajna za kola vremena porasta od 100 do 300ps.

Iako se novi materijali i metode mogu koristiti u budućnosti, uobičajena kola s vremenom porasta od 1 do 3 ns, razmak slojeva od 3 do 6 mil i FR4 dielektrični materijali su obično dovoljni za rukovanje vrhunskim harmonicima i dovoljno niskim prolaznim signalima, tj. , EMI uobičajenog načina rada može se smanjiti na vrlo nisku razinu.U ovom radu dat je primjer dizajna slojevitog slaganja PCB-a, a razmak slojeva se pretpostavlja da je 3 do 6 mil.

elektromagnetna zaštita

Sa tačke gledišta usmjeravanja signala, dobra strategija slojevitosti trebala bi biti postavljanje svih tragova signala u jedan ili više slojeva, koji su pored sloja napajanja ili uzemljenja.Za napajanje, dobra strategija slojevitosti treba da bude da je energetski sloj u blizini uzemljenja, a razmak između sloja napajanja i zemaljske ravni treba da bude što je moguće manji, što je ono što nazivamo strategijom „slojevanja“.

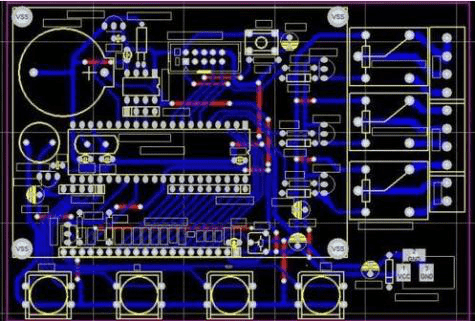

PCB stack

Koja strategija slaganja može pomoći u zaštiti i suzbijanju EMI?Sljedeća slojevita shema slaganja pretpostavlja da struja napajanja teče na jednom sloju i da su jedan napon ili više napona raspoređeni u različitim dijelovima istog sloja.Slučaj višestrukih slojeva moći će biti razmotren kasnije.

4-slojna ploča

Postoje neki potencijalni problemi u dizajnu 4-slojnih laminata.Prije svega, čak i ako je signalni sloj u vanjskom sloju, a snaga i uzemljenje u unutrašnjem sloju, udaljenost između sloja snage i uzemljenja je i dalje prevelika.

Ako je zahtjev za troškovima prvi, mogu se razmotriti sljedeće dvije alternative tradicionalnoj 4-slojnoj ploči.Oba mogu poboljšati performanse suzbijanja EMI-ja, ali su pogodna samo za slučaj kada je gustina komponenti na ploči dovoljno niska i ima dovoljno prostora oko komponenti (za postavljanje potrebnog bakrenog premaza za napajanje).

Prva je preferirana shema.Spoljni slojevi PCB-a su svi slojevi, a srednja dva sloja su slojevi signala/snage.Napajanje na sloju signala je rutirano širokim linijama, što čini impedanciju putanje struje napajanja niskom i impedanciju mikrotrakaste staze signala niskom.Iz perspektive EMI kontrole, ovo je najbolja 4-slojna PCB struktura dostupna.U drugoj shemi, vanjski sloj nosi snagu i uzemljenje, a srednji dva sloja nosi signal.U poređenju sa tradicionalnom 4-slojnom pločom, poboljšanje ove šeme je manje, a međuslojna impedancija nije tako dobra kao kod tradicionalne 4-slojne ploče.

Ako treba kontrolisati impedanciju ožičenja, gornja shema slaganja treba biti vrlo pažljiva da se ožičenje postavi ispod bakrenog ostrva napajanja i uzemljenja.Osim toga, bakreno ostrvo na napajanju ili sloju treba biti međusobno povezano što je više moguće kako bi se osigurala povezanost između DC i niske frekvencije.

6-slojna ploča

Ako je gustina komponenti na 4-slojnoj ploči velika, 6-slojna ploča je bolja.Međutim, efekt zaštite nekih šema slaganja u dizajnu 6-slojne ploče nije dovoljno dobar, a prolazni signal sabirnice napajanja nije smanjen.U nastavku se razmatraju dva primjera.

U prvom slučaju, napajanje i uzemljenje su postavljeni u drugi, odnosno peti sloj.Zbog visoke impedanse bakrenog napajanja, vrlo je nepovoljno kontrolisati EMI zračenje u zajedničkom modu.Međutim, sa stanovišta kontrole impedancije signala, ova metoda je vrlo ispravna.

U drugom primjeru, napajanje i uzemljenje postavljeni su u treći, odnosno četvrti sloj.Ovaj dizajn rješava problem bakrene impedancije napajanja.Zbog loše performanse elektromagnetne zaštite sloja 1 i sloja 6, diferencijalni mod EMI se povećava.Ako je broj signalnih linija na dva vanjska sloja najmanji, a dužina linija vrlo kratka (manje od 1/20 najveće harmonijske valne dužine signala), dizajn može riješiti problem diferencijalnog moda EMI.Rezultati pokazuju da je potiskivanje EMI diferencijalnog moda posebno dobro kada je vanjski sloj ispunjen bakrom, a područje obloženo bakrom uzemljeno (svakih 1/20 intervala valne dužine).Kao što je gore navedeno, polagat će se bakar

Vrijeme objave: Jul-29-2020